# Implementation of AES Algorithm on Micro **Blaze Processor in FPGA**

International Journal of Advanced Research in Computer and Communication Engineering

Santhosh Kumar. D<sup>1</sup>, K.Navatha<sup>2</sup>, Dr.Syed mushtak Ahmed<sup>3</sup>

M.Tech Student, Dept. Of Electronics and Communication Engineering, SR Engineering College, India Assistant Professor, Dept. Of Electronics and Communication Engineering, SR Engineering College, India<sup>2</sup> Professor & H.O.D, Dept. Of Electronics and Communication Engineering, SR Engineering College, India<sup>3</sup>

Abstract: In this paper The Advanced Encryption Standard was implemented with pure Hardware. However Field Programmable Gate Arrays (FPGAs) offer a more speed than existing implementations. This research investigates the AES algorithm with regard to 256 bits message length and 192 bits key length. In Spartan3 EDK we implemented the AES algorithm through pipelined architecture through the soft core processor Micro Blaze which in deed used for developing a Hardware structure which is configured using System C coding.

Keywords: Advanced Encryption Standard, FPGA, VHDL.

Vol. 2, Issue 10, October 2013

#### I. Introduction

government standard algorithm for encrypting and decrypting data. The standard is described in Federal Information Processing Standard (FIPS) 1997.

- 1.On January 2, 1997, The National Institute of Standards and Technology (NIST) published a request for comments for the "Development of a Federal Information Processing Standard for Advanced Encryption Standard."

- 2. NIST sought to "consider alternatives that offer a higher 2. Scramble each row (Shift Rows). level of security"

- 3. Than that offered by the Data Encryption Standard (DES), 4. Encrypt (Add Round Key). which grew vulnerable to brute-force attacks due to its 56-bit A term associated with AES is "the State," an 'intermediate effective key length.AES candidates were required to support a symmetric block cipher that supported multiple key lengths. The algorithm had to be publicly defined, free to use, and able to run efficiently in both hardware and software.

- 4. Fifteen AES candidate algorithms were announced in The main loop of AES9 performs the following functions:

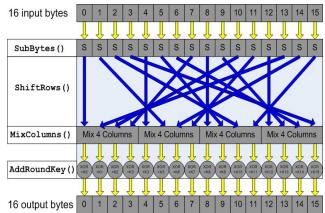

- Sub Bytes ()

- Shift Rows ()

- Mix Columns ()

- Add Round Key()

The first three functions of an AES round are designed to thwart cryptanalysis via the methods of "confusion" and "diffusion." The fourth function actually encrypts the data. Claude Shannon described the concepts of confusion and diffusion in his seminal 1949 paper, "Communication Theory of Secrecy Systems:"

AES is the Advanced Encryption Standard, a United States "Two methods suggest themselves for frustrating a statistical analysis. These we may call the methods of diffusion and confusion."10.

> Diffusion means patterns in the plaintext are dispersed in the cipher text. Confusion means the relationship between the plaintext and the cipher text is obscured.

> > A simpler way to view the AES function order is:

- 1. Scramble each byte (Sub Bytes).

- 3. Scramble each column (Mix Columns).

cipher,'11 or the cipher text before the final round has been applied.

AES formats plaintext into 16 byte (128-bit) blocks, and treats each block as a 4x4 State array. It then performs four operations in each round. The arrays contains row and column information used in the operations, especially Mix Columns () and Shift rows ().

#### II. AES ALGORITHM

AES is a symmetric block cipher with a block size of 128 bits. Key lengths can be 128 bits, 192 bits, or 256 bits;8 called AES-128, AES-192, and AES-256, respectively. AES- 128 uses 10 rounds, AES-192 uses 12 rounds, and AES-256 uses 14 rounds.

#### **2.1 Sub Bytes ():**

Sub Bytes () adds confusion by processing each byte through an S-Box. An S-Box is a substitution table, where

## International Journal of Advanced Research in Computer and Communication Engineering Vol. 2, Issue 10, October 2013

one byte is substituted for another, based on a substitution algorithm. Here is the AES Substitution is

#### 0 1 2 3 4 5 6 7 8 9 a b c d e f

To complete an S-Box operation on an example string of "ABC," take the hexadecimal value of each byte. ASCII "A" == hex 0x42, "B" == 0x43 and "C" == 0x44. Look up the first (left) hex digit in the S-Box column and the second in the S-Box row. 0x42 becomes 0x2c; 0x43 becomes 0x1a, and 0x44 becomes 0x1b.

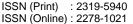

#### 2.2 Shift Rows ()

Shift Rows() provides diffusion by mixing data within rows. Row zero of the State is not shifted, row 1 is shifted 1 byte, row 2 is shifted 2 bytes, and row 3 is shifted 3 bytes, as shown in the *FIPS* illustration that follows:

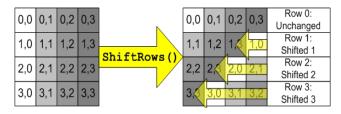

#### 2.3 Mix Columns ()

Mix Columns ()also provides diffusion by mixing data within columns. The 4 bytes of each column in the State are treated as a 4-byte number and transformed to another 4-byte number via finite field mathematics, as shown in the FIPS illustration that follows:

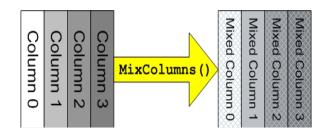

### 2.4 AddRoundKey ()

The actual 'encryption' is performed in the AddRoundKey () function, when each byte in the State is XORed with the subkey. The subkey is derived from the key according to a key expansion schedule, as shown in the *FIPS* illustration that follows:

#### 2.5 One Round of AES

Here is one round of AES encryption, shown in the FIPS publication two dimensionally:

#### III. AES DECRYPTION

Decryption occurs through the function AddRoundKey (), plus the inverse AES functions InvShiftRows(), InvSubBytes(), and InvMixColumns().AddRoundKey() does not require an inverse function, as it simply XORs the state with the sub key (XOR encrypts when applied once, and decrypts when applied again).

#### IV. IMPLEMENTATION

The Field Programmable Gate Array is majorly used for generation ASIC IC's to the computations. They offer more speed in execution process. SO, for generation ASIC IC's FPGA's are majorly used. The 64 FFT with radix 4 is simulated and synthesized as well as implemented on the FPGA of below configuration.

### International Journal of Advanced Research in Computer and Communication Engineering Vol. 2, Issue 10, October 2013

Table3.1: Configuration of FPGA

| Property Name | Value     |

|---------------|-----------|

| Family        | Spartan 3 |

| Device        | XC3S200   |

| Package       | TQG144    |

| Speed Grade   | -4        |

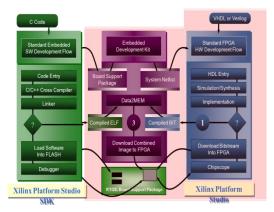

#### 4.1 Xilinx Platform Studio

The Xilinx Platform Studio (XPS) is that the development atmosphere or user interface used for planning the hardware portion of your embedded processor system. B. Embedded Development Kit Xilinx Embedded Development Kit (EDK) is associate integrated software system tool suite.

For developing embedded systems with Xilinx MicroBlaze and PowerPC CPUs. EDK includes a spread of tools associated applications to help the designer to develop associate embedded system right from the hardware creation to final implementation of the system on an FPGA. System style consists of the creation of the hardware and software systemparts of the embedded processor system and also the creation of a verification element is elective. A typical embedded system style project involves: hardware platform creation, hardware platform verification (simulation), software system platform creation, software system application creation, and software system verification. Base System Builder is that the wizard that's wont tomechanically generate a hardware platform in keeping with the user specifications that's defined by the MHS (Microprocessor Hardware Specification) file.

The MHS file defines the system design, peripherals and embedded processors]. The Platform Generation tool creates the hardware platform mistreatment the MHS file as input. The software system platform is defined by MSS (Microprocessor software system Specification) file that defines driver and library customization parameters for peripherals, processor customization parameters, customaryone hundred ten devices, interrupt handler routines, and differentsoftware systemconnected routines. The MSS file is associate input to the Library Generator tool for personalisation of drivers, libraries and interrupts handlers.

Figure 4.1: Embedded Development Kit Design Flow

The creation of the verification platform is facultative and is predicated on the hardware platform. The MHS file is taken as Associate in Nursing input by the Siegen tool to make simulation files for a particularmachine. 3varieties of simulation models will be generated by the Siegen tool: behavioral, structural and temporal arrangement models. Anotherhelpful tools on the market in EDK ar Platform Studio that provides the GUI for making the MHS and MSS files. Produce / Import IP Wizard that permits the creation of the designer's own peripheral and import them into EDK comes. Platform Generator customizes and generates the processor system within thesort of hardware net lists. Library Generator tool configures libraries, device drivers, file systems and interrupt handlers for embedded processor system. Bit stream Initializer tool initializes the instruction memory of processors on the FPGA shown in figure 2. antelope Compiler tools are used for collection and linking application executable for every processor within the system [6]. There are 2 choices on the market for debugging the appliance created victimization EDK namely: the compiler getting used for the processor. C. package Development Kit Xilinx Platform Studio package Development Kit (SDK) is Associate in Nursing integrated development atmosphere, complimentary to XPS, that's used for C/C++ embedded package application creation and verification. SDK is made on the Eclipse open source framework. Soft Development Kit (SDK) may be a suite of tools that allows you to style a package application for elite Soft IP Cores within the Xilinx Embedded Development Kit (EDK). The package application will be written during a "C or C++" then the entire embedded processor system for user application are completed, else correct&download the bit file into FPGA. Then FPGA behaves like processor implemented on it in a Xilinx Field Programmable Gate Array (FPGA) device.

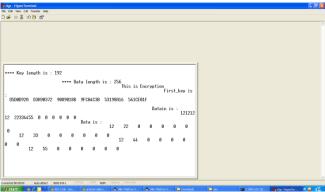

Hardware implementation was through system C coding and its results are as follows

ISSN (Print) : 2319-5940 ISSN (Online) : 2278-1021

### International Journal of Advanced Research in Computer and Communication Engineering Vol. 2, Issue 10, October 2013

Fig: FPGA sent data was seen in pc through HyperTerminal

Fig: Synthesis report

#### **V CONCLUSION**

In this work advanced encryption algorithm was implemented using FPGA. This system works on a period pipelined flow on the micro blaze architecture of Spartan 3 EDK. On the opposite hand synthesis results show that space consumption is low, using simply100 percent of logic components of FPGA for AES, permitting the implementation of this method over inexpensive FPGAs.

#### REFERENCES

- [1] DAEMEN, J. AND RIJMEN, V., The design of Rijndael: AES TheAdvanced Encryption Standard. Springer-Verlag, 2002.

- [2] SCHNEIER, B., Applied Cryptography: Protocols, Algorithms and SourceCode in C. John Wiley & Sons, Inc. 2nd Ed, 1996.

- [3] GOMES, O. S. M.; PIMENTA, T. C.; MORENO, R. L., "A Highly Efficient FPGA Implementation", 2nd Latin America Symposium on Circuits and Systems (LASCAS-2011), February 2011.

- [4] DAEMEN, J. AND RIJMEN, V. A Specification for The AES Algorithm.NIST (National Institute of Standards and Technology).http://csrc.nist.gov/archive/aes/rijndael/wsdindex.html, 2010.

- [5] Ahmad, N.; Hasan, R.; Jubadi, W.M; "Design of AES S-Box using combinational logic optimization", IEEE Symposium on IndustrialElectronics & Applications (ISIEA), pp. 696-699, 2010.

- [6] Alex Panato, Marcelo Barcelos, Ricardo Reis, "An IP of an AdvancedEncryption Standard for Altera Devices", SBCCI 2002, pp. 197-202, Porto Alegre, Brazil, 9 and 14 September 2002.